从代码到芯片 软件开发视角下的计算机组成原理

对于许多软件开发工程师而言,计算机组成原理常被视为一个遥远而艰深的底层领域,仿佛是硬件工程师的专属领地。深入理解计算机的组成——从中央处理器到存储器层次,从指令系统到输入输出机制——并非学术上的苛求,而是成为一名卓越软件工程师的必经之路。它解答的正是我们每天编写的代码最终如何被物理机器理解和执行这一根本问题。理解组成原理,能让开发者写出更高效、更健壮、与硬件特性更契合的软件。

一、处理器(CPU):代码执行的终极舞台

在软件开发中,我们谈论算法时间复杂度,但最终决定性能的,是代码如何在CPU上运行。CPU的组成——运算器、控制器、寄存器——直接对应着高级语言中的运算、控制流和变量。

- 指令集架构(ISA):这是软件与硬件的契约。无论是x86、ARM还是RISC-V,开发者编写的代码(即便是高级语言)最终都会编译成该CPU能理解的指令序列。理解指令的类型(运算、访存、控制)、寻址方式以及流水线机制,有助于在编写高性能代码(如C/C++内联汇编、理解编译器优化)时做出更明智的选择。例如,了解CPU缓存行(Cache Line)的大小和内存对齐要求,可以显著优化数据密集型应用的性能。

- 流水线与超标量:现代CPU通过流水线并行执行多条指令。分支预测失败导致的流水线清空,是性能的隐形杀手。这启示开发者在编写关键循环或条件判断密集的代码时,需要注意分支的可预测性,有时甚至需要为了“讨好”分支预测器而调整代码结构。

- 多核与并发:从组成原理的角度理解多核CPU的缓存一致性协议(如MESI)、内存屏障和原子操作,是构建正确、高效多线程程序的基础。这解释了为何无锁编程如此复杂,以及Java中的

volatile关键字或C++中的内存序(memory_order)背后真正的硬件含义。

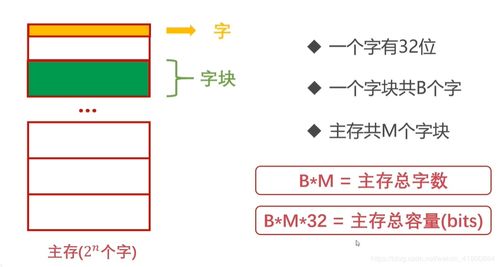

二、存储器系统:数据的时空博弈

开发者眼中的“内存”,在组成原理中是一个层次化的金字塔:寄存器、高速缓存(L1/L2/L3)、主存(DRAM)、辅存(磁盘/SSD)。这个层次结构的核心目标是弥补CPU高速与存储器低速之间的巨大鸿沟。

- 局部性原理:这是存储器层次设计的灵魂,也应成为高性能编程的灵魂。时间局部性(刚刚访问的数据很可能再次被访问)鼓励我们重用变量和对象;空间局部性(访问某个地址后很可能访问其相邻地址)鼓励我们使用连续存储的数据结构(如数组而非链表)。编写缓存友好(Cache-Friendly)的代码,往往能带来数量级的性能提升。

- 虚拟内存:这是操作系统提供的关键抽象,但其硬件基础是内存管理单元(MMU)。理解分页机制、TLB(转址旁路缓存)的工作原理,能帮助开发者理解程序内存访问的代价,以及为何在性能敏感场景下,减少缺页中断和TLB未命中至关重要。

三、输入输出系统:与世界的接口

软件的价值在于处理输入并产生输出。I/O系统的组成原理决定了软件与外部设备交互的效率和方式。

- 程序查询、中断与DMA:从效率极低的循环等待(程序查询),到允许CPU并行工作的中断驱动I/O,再到彻底解放CPU的直接存储器访问(DMA),硬件技术的演进直接推动了异步编程、事件驱动等软件范式的兴起。理解这些,能让我们更深刻地领会Node.js的I/O模型或Linux的

epoll机制背后的硬件逻辑。 - 总线与接口:虽然对上层应用透明,但总线的带宽和协议(如PCIe)是系统I/O性能的瓶颈。在开发数据库、视频处理等I/O密集型应用时,必须对此有清晰的认知。

四、系统总线:计算机的“神经系统”

总线连接所有组件,其带宽和仲裁机制影响着系统整体性能。在多核、多设备协同的现代系统中,理解总线竞争有助于诊断复杂的性能瓶颈。

软硬协同,方得始终

计算机组成原理并非软件开发的对立面,而是其坚实的地基。从用高级语言描述算法,到思考数据在缓存中的布局;从编写多线程程序,到理解底层的内存一致性模型;从调用一个简单的文件读取API,到知晓其可能触发的DMA与中断流程——这个过程,正是软件思维与硬件现实的深度融合。

“搞定”组成原理,对软件开发者而言,并非要成为硬件设计师,而是要建立一种系统化的思维模型。这种模型让我们能透过高级语言的抽象,洞悉代码在真实机器上的行为,从而在性能优化、问题调试和架构设计时,做出既有高度又接地气的决策。当你能清晰地想象出你的每一行代码如何驱动晶体管运转时,你便获得了一种构建可靠、高效数字世界的强大能力。

如若转载,请注明出处:http://www.ooaecad.com/product/28.html

更新时间:2026-04-20 13:48:11